��B��Ƭ�CӲ�����ɔ_���

�M�����^������ṩij�N��ʽ�����ᡣ

ʹ�ÝM��ϵ�yҪ�������l�ʕr犡�

�r犮a�����M����������ԓ�r犵�������ʯӢ���w��ʎ���⚤Ҫ�ӵء�

�õؾ����r犅^Ȧ�������r犾��M���̡�

I/O���·�M������ӡˢ��߅����M���x�_ӡˢ�塣���M��ӡ�ư����̖Ҫ�ӞV�����ĸ����^������̖ҲҪ�ӞV����

�ô��K�������k�����pС��̖���䡣

�ô��K�������k�����pС��̖���䡣MCD�o�ö�Ҫ�Ӹߣ���ӵأ����x��ݔ���ˣ������·��ԓ���Դ�صĶ˶�Ҫ�ӣ���Ҫ�ҿա�

�e�ò��õ��T�·ݔ��˲�Ҫ�ҿգ��e�ò��õ��\����ݔ��˽ӵأ�ؓݔ��˽�ݔ���ˡ� (10) ӡ�ư�M��ʹ��45�۾�������90�۾������ԜpС���l��̖����İl���c��ϡ�

ӡ�ư尴�l�ʺ�����_�P���Էօ^����Ԫ���c����Ԫ��Ҫ���x���h

��

���������p����Æ��c���Դ�͆��c�ӵء��Դ�����ؾ��M���֣��������ܳ��ܵ�Ԓ�ö��Ӱ��ԜpС�Դ���ص�����늸С�

�r犡�������Ƭ�x��̖Ҫ�h�xI/O���ͽӲ����

ģ�M늉�ݔ�뾀������늉���Ҫ�M���h�x�����·��̖�����e�Ǖr犡�

��A/D����������ֲ����cģ�M�����ɽyһ��Ҳ��Ҫ���档

�r犾���ֱ��I/O����ƽ��I/O���ɔ_С���r�Ԫ�����_�h�xI/O��|��

Ԫ�����_�M���̣�ȥ��������_�M���̡�

�P�I�ľ�Ҫ�M���֣����ڃ�߅���ϱ��o�ء����پ�Ҫ��Ҫֱ��

�������еľ���Ҫ�c������������_�P��ƽ�С�

ʯӢ���w�����Լ��������е��������治Ҫ�߾���

����̖�·�����l�·�܇���Ҫ�γ�����h·��

��̖����Ҫ�γɭh·���粻�ɱ��⣬�h·�^�M��С��

��̖����Ҫ�γɭh·���粻�ɱ��⣬�h·�^�M��С��ÿ�������·һ��ȥ����ݡ�ÿ��늽����߅�϶�Ҫ��һ��С�ĸ��l��·��ݡ�

�ô��������g��ݻ�ۿ���ݶ�����늽�������·���늃�����ݡ�ʹ�ùܠ���ݕr���⚤Ҫ�ӵء��ݣ�Դ��늣��ӣ��W�������ṩ���g֧��

���ĵ�ַ��http://m.jssjbk.com/dz/26/2010626221958.shtml

���Ę˺�:

- ��һƪ���£���B˾�C�ƾ��z�y�������·�D

- ��һƪ���£�distributed control system Details

-

���ֽ̳̣���Ƭ�C�ČW�����`���E

���ֽ̳̣���Ƭ�C�ČW�����`���E

�\�Æ�Ƭ�C�����˽��Ƭ�CӲ���Y�����Լ��Ȳ��YԴ���\�ã��څR����C�Z���ЌW�����N���õij�ʼ���O�ã��Լ���ɸ��N���õij����ơ� �\�ð��oݔ����̖���l����O���@�Fݔ��

�P�I�~��51��Ƭ�CPIC��Ƭ�C��Ƭ�C ���ٙ�Ŀ���OӋ���� -

���Æ�Ƭ�C���FCAN�����cLIN�����g�Ă�ݔ�OӋ����

���Æ�Ƭ�C���FCAN�����cLIN�����g�Ă�ݔ�OӋ����

�F���������g�ѽ��V�������ڹ��I�����У�������CAN��Controler��Area��Nerwork���������ھ��пɿ��Ըߡ��ɱ��͡������F�ȃ��c���ڬF���������H���̑�����ռ�����^����~��

�P�I�~����Ƭ�C ���ٙ�Ŀ���OӋ���� -

�W����Ƭ�C�ɲ�����ֻ��ܛ��������������

�W����Ƭ�C�ɲ�����ֻ��ܛ��������������

�ҵĴ��ǣ�������ԭ�����£�һ��ܛ����������ڽ̌W���Ѹ��ྫ������ܛ���Č��F�����ڌW���W���r�g���F������һ�׆�Ƭ�C�����ֱ��^���r�g�����Ҍ���Ŀ̫�࣬���Ԟ���

�P�I�~��PIC��Ƭ�C51��Ƭ�C��Ƭ�C ���ٙ�Ŀ���OӋ���� -

�����x�����m�ϵĆ�Ƭ�C

�����x�����m�ϵĆ�Ƭ�C

�������ց��f�����ȸ����Լ��W��ʲô�ӆ�Ƭ�C���xʲô��͵Ć�Ƭ�C����Ϥʲô��͵Ć�Ƭ�C���xʲô��͵Ć�Ƭ�C������Ƭ�C���HҪ�OӋ�·��߀Ҫ�OӋ����ܛ�����x�Լ���Ϥ�Ć�Ƭ�C������죬Ҳ�����@�óɹ��������B����x�����m�ϵĆ�Ƭ�C��

�P�I�~�� ���ٙ�Ŀ���OӋ���� -

��Ƭ�C�����������ʲô

��Ƭ�C�����������ʲô

��Ƭ�C�����������ʲô

�ڳ��W��Ƭ�C�ĕr���ǰ��S�ܶ����P�ھ���Ć��}���䌍���������ͬ�˵����K����ѪҺ���}�����ц�Ƭ�C�ľ����}�������ˣ�51��Ƭ�C���������}

�P�I�~��51��Ƭ�CPIC��Ƭ�C��Ƭ�C ���ٙ�Ŀ���OӋ���� -

��keilܛ��������Ƭ�C����IJ��E

��keilܛ��������Ƭ�C����IJ��E

Keil��Ƭ�C����ܛ��Keil C51�dž�Ƭ�CC�Z��ܛ���_�lϵ�y���c�R����ȣ�C�Z���ڹ����ϡ��Y���ԡ����x�ԡ��ɾS�o���������@�ă��ݣ�����W���á�Keil�ṩ�˰���C���g������R

�P�I�~��51��Ƭ�CPIC��Ƭ�C ���ٙ�Ŀ���OӋ���� -

Ԕ��51��Ƭ�C�\���^��

Ԕ��51��Ƭ�C�\���^��

Ԕ��51��Ƭ�C�\���^�� ע��1.ROM��ֻ�x�惦������Ƭ�C��ֻ�x�惦�^������ڴ惦������ַQ����惦����51��Ƭ�C��EPROM�����^��EPROM�ǿɲ�����ֻ

�P�I�~�� ���ٙ�Ŀ���OӋ���� -

pic��Ƭ�C��c51��ʲô�^�e

pic��Ƭ�C��c51��ʲô�^�e

pic��Ƭ�C��c51��ʲô�^�e(�^�e1)�����Y��:MCS-51��Ƭ�C�Ŀ����Y�����T-�Z������,Ӌ��C��ͬһ���惦���gȡָ��͔���,���߲���ͬ�r�M��;��PIC��Ƭ�C�Ŀ����Y���ǹ���Y��

�P�I�~����Ƭ�CPIC��Ƭ�C51��Ƭ�C ���ٙ�Ŀ���OӋ���� -

51��Ƭ�C���F���ϼ���Q�k��

51��Ƭ�C���F���ϼ���Q�k��

��������51��Ƭ�C���F���ϼ���Q�k����Ԕ�����£�

���ϬF������һ����Ƭ�C�ضȱO�yϵ�y������C��һ������������оƬ�o�����������P�·��D�� ��51��̎����������·��

�P�I�~����Ƭ�C51��Ƭ�C ���ٙ�Ŀ���OӋ���� -

PIC��Ƭ�C�R���Z��ָ��Ԕ��

PIC��Ƭ�C�R���Z��ָ��Ԕ��

PIC��Ƭ�C�R���Z��ָ��Ԕ��

pic��Ƭ�C����Æ�Ƭ�C֮һ���S����������pic��Ƭ�C�M���_�l����ˣ��쾚pic��Ƭ�C�����Ȟ���Ҫ���鱣�C����ܜʴ_���쾚����pic��Ƭ�C��ʹ

�P�I�~��PIC��Ƭ�C��Ƭ�C ���ٙ�Ŀ���OӋ���� -

���N51��Ƭ�C�������d������B

���N51��Ƭ�C�������d������B

���N51��Ƭ�C�������d������B

һ��ֻ��ͨ�^���N��ʽ���d����Ƭ�C�У�1.JTAG 2.ISP 3.IAP1.JTAGҪʹ��JTAG��ʽ���d��������ʹ��J-LINK��ULINK��ST-LINK��ֻ��Ҫ��

�P�I�~��PIC��Ƭ�C51��Ƭ�C��Ƭ�C ���ٙ�Ŀ���OӋ���� -

��Ƭ�C��I2Cͨ���OӋ

��Ƭ�C��I2Cͨ���OӋ

I2Cÿһλ��̖�ĕr�����̣���I2Cͨ�����ֹ����Ă�ݔ�У�Ҳ�й̶��ĕr��Ҫ��I2Cͨ�ŵ���ʼ��̖��Start��������Ҫ�l��һ���ęC�ĵ�ַ���@����ַһ���� 7λ���o�����ĵ� 8

�P�I�~��PIC��Ƭ�C51��Ƭ�C��Ƭ�C ���ٙ�Ŀ���OӋ���� -

AT89C51��Ƭ�C��RS232-GPIB�������OӋ

AT89C51��Ƭ�C��RS232-GPIB�������OӋ

Խ��Խ��Ĝy���x���ṩGPIB��General Purpose Intefface Bus�������ӿڣ�ͨ�^ԓ�������Է����ݵ��B�ӎ���GPIB�ӿڵăx����Ӌ��C���M��һ��GPlB�W�j��GPIB�O���cӋ��C�B

�P�I�~��PIC��Ƭ�C51��Ƭ�C��Ƭ�C ���ٙ�Ŀ���OӋ���� -

��Ƭ�C����������Լ�ԭ������

��Ƭ�C����������Լ�ԭ������

ÿ����Ƭ�Cϵ�y�ﶼ�о���ȫ���ǽо��w��ʎ�����چ�Ƭ�Cϵ�y�ᄃ������÷dz������Y�φ�Ƭ�C�Ȳ����·���a����Ƭ�C����횵ĕr��l�ʣ���Ƭ�C��һ��ָ��Ĉ��ж��ǽ���

�P�I�~��51��Ƭ�CPIC��Ƭ�C��Ƭ�C ���ٙ�Ŀ���OӋ���� -

�����λ���چ�Ƭ�C����׃�l���еđ���

�����λ���چ�Ƭ�C����׃�l���еđ���

����׃�l�{�����齻��늙C�{�ٵ���Ҫ�ֶ��ѽ��ڹ��I�I���Б��õ�ʮ�֏V��������е��{�ٷ����������پ��ȸߡ��ӑB푑��졢�m�÷����V���\�пɿ��ȼ��g���ܣ�����ȡ��ֱ��

�P�I�~����Ƭ�C׃�l�� ���ٙ�Ŀ���OӋ���� -

����Æ�Ƭ�C��������ܴa�i�·

����Æ�Ƭ�C��������ܴa�i�·

����ܴa�i����ݔ���ܴa��ʽ�IJ�ͬ�ɷ֞�ö�N��������õ�һ�N���Ô����I�Pݔ���ܴa������ܴa�i���@һ�v��Ҫ��B��ATmega8��LCD1602Һ���@ʾ���ȽM�ɵ�����ܴa�i���@

�P�I�~����Ƭ�C ���ٙ�Ŀ���OӋ���� -

��Ƭ�C����LED�����·

��Ƭ�C����LED�����·

1������΄���D��ʾ���Oҕ�_�PK1������P3.0�˿��ϣ����ðl����O��L1�����چ�Ƭ�CP1.0�˿��ϣ��@ʾ�_�P��B������_�P���ϣ�L1�����_�P���_��L1Ϩ�硣2���·ԭ��D3��ϵ�y

�P�I�~����Ƭ�CLEDLED�·�D ���ٙ�Ŀ���OӋ���� -

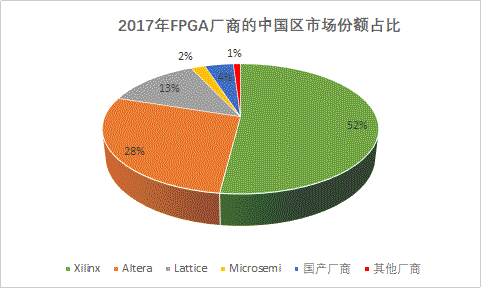

��Ԕ����FPGAоƬ���x(�D��)

��Ԕ����FPGAоƬ���x(�D��)

���գ���ý�w����Q��������Ӽ��g�о�����ǰ�ɹ����Ƴ������ׂ������ɿص����ǧ�f�T�������ܸ߿ɿ�FPGA���F���ɾ����T��У�оƬ��FPGAһֱ�LJ��ȵĶ̰壬�Ј�������

�P�I�~����Ƭ�C ���ٙ�Ŀ���OӋ���� -

��Ƭ�CҪ�@ô�W���˗l֔ӛ!

��Ƭ�CҪ�@ô�W���˗l֔ӛ!

��ô�W��Ƭ�C��Ҳ�����������f�W�˺Îׂ��¿ɾ��Ǜ]��ʲô�Mչ����Ȼ��������ÿ�����ܵ��Ľ���ˮƽ��ͬ�͂������������IJ���W��������п���֮�֣����Ҹ��X���صľ��njW

�P�I�~����Ƭ�C ���ٙ�Ŀ���OӋ���� -

��Ƭ�C������ܼĴ���(�D��)

��Ƭ�C������ܼĴ���(�D��)

�چ�Ƭ�C����һЩ�����Ĵ惦��Ԫ���Á������@Щ�����ģ����Q֮������ܼĴ�����SFR��������<����ܼĴ�����ַӳ�����һ��>����<����ܼĴ�����ַӳ���������>����<

�P�I�~����Ƭ�C�Ĵ��� ���ٙ�Ŀ���OӋ����

������dȤ��

- ���]����

- ������

-

- �oԴ�����x�� 2024-10-10

- ACM6755 ֧��3�������õ�ȫ��������ֱ���oˢ늙C��IC���� 2024-10-09

- YXC�����Q�����������I���C���� 2024-09-27

- ��Դ����͟oԴ����ą^�e 2024-09-24

- ��ģ�K��Ȳ��p����ѕr�lCP-��־��� 2024-09-20

- ���w�C�����Ĺ���ԭ�� 2024-09-19

- YXCʯӢ��Դ��ֿɾ��̾����l�c200MHZ��С���c�ɾ��_����6λ��������5G��վ 2024-09-12

- 70V�͉����{OVP�ֵ���^�����oо-ƽоPW1600 2024-09-05

- YXC�P�d��Դ��Ʒ�l��ح1.2V�����ĕr犽�Q���� 2024-09-05

- YXC�P�d | 32.768KHZ�����x�ͷ��� 2024-09-02

- ���T�˺�

-

���ż����· ������·�D LED ���l�Ŵ����·�D ��Ƭ�C 늙C���� LED�·�D �����Դ �_�P�����Դ ����·�D ׃�l�� ��׃�� LED�����· ���{�S���g LED���·�D AV�Ŵ����· �ص����·�D 555���r�� 늴Št�·�D ���������· 51��Ƭ�C �·�OӋ �^�����o�· �^�����o�· �����· �ھ�Ӌ�� ���˷����· ��·���o�· �ŷ�늙C ���M늙C PIC��Ƭ�C ֱ�������Դ ���{�����Դ EMC ©늱��o�· Ƕ��ʽϵ�y ��Ȧ ���l��׃�� ���� ���{ UPS DC-DC�· �ضȂ����� 늴ż��� ���� ���l�_�P�Դ ���� EMI ��˹�� ���⾀