����FPGA��32λǶ��ʽ̎�����Ľ�Q����

�҂����քe��һ�¿�����IP�Ⱥ˝M����͑�������Ҫ������N��̫�W��ϵ�y�����ӡ�ÿ�N�OӋ���в�ͬ��ϵ�y�ܘ�:����̎�������á���̫�W MAC IP�����Լ��惦���ӿڡ����⣬�@Щ����߀ͻ���˿��c�@ЩӲ����ϵ�y���ʹ�õIJ�ͬTCP/IPܛ���f�h��������Ӳ������ģ�K��ܛ���Ӷ��ǿɶ��Ƶģ���������Ը������õ���Ҫ���@Щϵ�y�M�����p��

������̫�W��ϵ�y

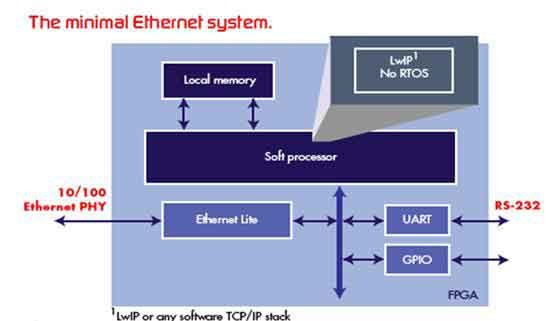

�����h�̱Oҕ����Ƒ���������Ҫ�ĺ��ξW�j�ӿځ��f����D3��ʾ����С���W�j��ϵ�y������ˡ��ڴ�����У�TCP/IP����Ҫ���^��(<1Mbps)�����LwIP(�����滥�W�f�h��)�@�ӵ�СTCP/IP�f�h��(����ҪRTOS���r����ϵ�y)������ˡ�

�D3��Ҏģ��С����̫�Wϵ�y��

�@����ʹ�ò��g�����̫�WLite IP�ں��εIJ�ԃģʽ���F��ȫ��ܛ�����������εđ��Ìӣ���ȫ���惦��FPGA�еı��ش惦���С���D3����ʾ��������Ҫ��I/O�ӿڣ�RS-232 UART��GPIO���������ӵ�������ϵ�y�С�

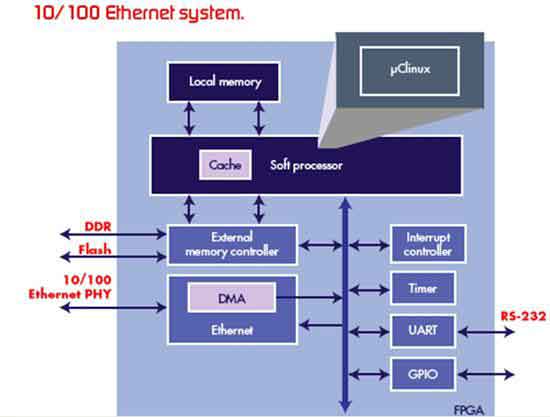

�D4�����͵�10/100��̫�Wϵ�y�ܘ���

ͨ�^���D3�е���Сϵ�y��һ�����ģ����Ԍ��F����TCP/IP��������(10-50Mbps)�����D����D4��ʾ�ĸ�����͵�10/100��̫�W��Q��������Ҫ��׃���У�

1. ����̫�WMAC����ֱ�Ӵ惦���L��(DMA)���棬���F�Д��ӣ�

2. ��ϵ�y�����ⲿ�惦������̎�������Ӿ��棻

3. �����s��TCP/IP������Linux(Clinux)ϵ�yTCP/IP�f�h����

������Ҫ100Mbps����TCP/IP���������đ��ã����Կ��]ӲIP��ܛIP�Ⱥ˷�ʽ�ṩ����ģʽ��̫�WMAC(�D5)����@�ø߶ˑ�������Ҫ��500Mbps���ϵ�������������Ҫ���ɢ/�R��DMA(SGDMA)�ȸ�DMA���g���Լ�����������������(DRE)��У��ж�d (CSO)��FPGAӲ�����������g��

��M��ǧ����̫�W�����ߔ��������ʵ���������Ҫ�������ܵ�Ƕ��ʽ(Ӳ)̎������FPGA�ό��F�Ŀɶ���ܛ̎�������Լ�����ľ��_��������16Kbitָ��͔������档��ܛ��ƽ�_���f��Linux��VxWorks��Integrity��QNX��ܛ��ƽ�_�еĸ�TCP/IP��֧���T���㿽ؐ��У����·�ȹ��ܡ�

����Ӳ����ܛ���ڃȵ��S�����ض���Ӱ푵�TCP���ܣ����M��Ӱ�ϵ�yTCP�����������@Щ���ذ�����

1. ̎�����������l�ʡ����ܺ;���

a. �l�ʣ�TCP/IP�f�hͨ����Ҫ���d�ɏ��Ñ����濽ؐ���f�h�����Ƶľ��棬Ȼ���ٌ��俽ؐ����̫�WMAC��FIFO��ȥ���@Щ�惦����ؐ������Щ����ܛ����ʽ��ɵģ������Ҫ̎������̎�����ڡ�ͬ�r̎����߀���cTCPУ�͵�Ӌ�㣬Ӌ���^������Ҫ�������������Ĵ惦���x���������̎������ϸ���Ĵ惦�����ڸ��̵ĕr�g������@Щ�������Ķ����Ա����^�ߵĔ������ʣ�

b. ���ܣ�TCP/IP�f�h����Ҫ���������İ��^���d���M���L��̎����������^̎����һ���֣����͵��L�������xȡ���^��Ϣ���ض�λ�����ÿ����������̎���^�̶���Ҫ�ஔ�����λ������������̎��ÿ���������r����Ҫ�M�г˷��������ڿ����õ�̎�����У�����_�������λ��˷���ָ����ܫ@�ø��ߵ����ܣ�

c. ���棺����������̫�WMAC����ؐ���惦����֮����ͨ�^TCP/IP�f�h���IJ�ͬ�ӡ�Ȼ��TCP/IP���еĔ�����̎�����a�������С������д��a�͔������x�������Е�������̎����Ч�ʲ������̫�W������

2. �惦��

�惦���L���r�g�����t����ϵ�y�����о��Ӱ푡����͑����У�TCP/IP���ò����惦�ڱ��ش惦���У�����͔����惦���ⲿ�惦���С���ȡ������ָ�������M�ĕr�g���������кܴ�Ӱ푡��惦������ͨ���c�����С���P�����ָ��͔��������С�����ڜp�p�ⲿ�惦�����t�ʹ�ȡ�r�g��������Ӱ푡�

3. ��̫�WMAC

��FPGA�Ќ��F����̫�WMAC���O�ṩ�˺ܴ���`���ԣ��e���ڹ���ģʽ(�oDMA�cSGDMA)��������FIFO��ȡ�DRE֧�֡�CSO֧���Լ�����֧�ַ��档ÿһ헶���Ӱ푵�MAC����Ҫ���YԴ���Լ����܉��̎���������Ĺ��ܶ��٣��Ķ������w�������Ӱ푡�

4. TCP/IP�f�h��

�`��ă���TCP/IP�f�h����Ӱ�ϵ�y���ܵ���Ҫ���ء���Ӳ��CSO���㿽ؐAPI(��������Ҫ�đ��ÿ�ؐ���f�h������)�Լ������×��x헵�TCP/IP�����ܵ�֧�ֿɎ������ϵ�y���ܡ�

5. ��Ϣ����

��Ϣ(���Ô���)�Ĵ�С��Ӱ����ܵ���һ�����ء��S����Ϣ�p�٣�TCP/IP�f�h�^(��TCP��IP����̫�W�^)���_�N���ӣ��Ķ����pС���w�Ĕ����d������������

��������Ì��ڳɱ������ܺ��ܶ���һ�M�������������ض������OӋ�aƷ�r���OӋ�ˆT������@Щ����֮�g�M�����_�����ԣ�Ȼ���������m���Ј��l�����@ЩҪ���ڮaƷ�������ڃȿ��ܕ��l��׃���������`������õ�ƽ�_�܉��ڲ���׃�OӋƽ�_���̵���r�¸�����Ҫ���@ЩҪ���M������ƽ�⡣�ݣ�Դ��늣��ӣ��W�������ṩ���g֧��

���ĵ�ַ��http://m.jssjbk.com/dz/22/15469290073071.shtml

���Ę˺�:

- ��һƪ���£����̎����8���·�OӋ����

- ��һƪ���£���Ƭ�C�cPT1000�ضȂ��������F�L�C�ضȿ���ϵ�y���OӋ

-

����FPGA�������F���l�I���{���·���OӋ�ͷ�����C��

����FPGA�������F���l�I���{���·���OӋ�ͷ�����C��

������̖��ݔϵ�y�֞������ݔϵ�y���l����ݔϵ�y���l����ݔϵ�yҲ�Д����{��ϵ�y�������{����̖�ַQ���I����̖�������{���^����̎�����ǔ�����̖�����d����������l�ʺ���

�P�I�~�� ���ٙ�Ŀ���OӋ���� -

��Ξ�Ƕ��ʽϵ�y�x������ĵ�������

��Ξ�Ƕ��ʽϵ�y�x������ĵ�������

�OӋ����MCU�������ף�Ҳ�]�О������ض�Ƕ��ʽ�OӋ�x����m��MCU���S���ض��ڑ��õ�ע����헶��������ã��@ʹ�ñ��^MCUҎ������������ԡ����ķ������ڷ���������MCU��

�P�I�~�� ���ٙ�Ŀ���OӋ���� -

��Ԕ����FPGAоƬ���x(�D��)

��Ԕ����FPGAоƬ���x(�D��)

���գ���ý�w����Q��������Ӽ��g�о�����ǰ�ɹ����Ƴ������ׂ������ɿص����ǧ�f�T�������ܸ߿ɿ�FPGA���F���ɾ����T��У�оƬ��FPGAһֱ�LJ��ȵĶ̰壬�Ј�������

�P�I�~����Ƭ�C ���ٙ�Ŀ���OӋ���� -

Ƕ��ʽϵ�y�Ĺ���ԭ���͑���

Ƕ��ʽϵ�y�Ĺ���ԭ���͑���

Ƕ��ʽϵ�y�Ĺ���ԭ���͑��á���Ӌ��C����20���o���������İl��֮һ������Ҳ���~���PC�r������PC�r���ĵ���Ҳ��־��Ƕ��ʽ�aƷ���Q�������֙C��PDA�����ؙC���ȡ�

�P�I�~��Ƕ��ʽϵ�y��Ƭ�C ���ٙ�Ŀ���OӋ���� -

Ƕ��ʽ�R���Z�ԌW�����

Ƕ��ʽ�R���Z�ԌW�����

������c��һ���Ŀ����Ҫ��Ƕ��ʽ�R�����yԇ���R�������^��C����Ҳ���^�����nj�����������팑߀�ǵ�һ�Σ���ȫ�]�и��ֻ���ϾW���Y�ϣ��Լ����������������Լ�һ

�P�I�~�� ���ٙ�Ŀ���OӋ���� -

ՄՄǶ��ʽϵ�y�����c����Ԕ����B

ՄՄǶ��ʽϵ�y�����c����Ԕ����B

-

ʲô��Ƕ��ʽϵ�y��ʮ����

ʲô��Ƕ��ʽϵ�y��ʮ����

-

��BJavaǶ��ʽϵ�y�_�l

��BJavaǶ��ʽϵ�y�_�l

-

Ƕ��ʽϵ�y|Ƕ��ʽLinux�_�l����

Ƕ��ʽϵ�y|Ƕ��ʽLinux�_�l����

-

Ƕ��ʽܛ���_�l|�lչڅ��

Ƕ��ʽܛ���_�l|�lչڅ��

-

ʲô��Ƕ��ʽϵ�y

ʲô��Ƕ��ʽϵ�y

-

Ƕ��ʽϵ�yԔ����B

Ƕ��ʽϵ�yԔ����B

-

����Ƕ��ʽϵ�y|�����~�R��2

����Ƕ��ʽϵ�y|�����~�R��2

-

����Ƕ��ʽϵ�y|�����~�R��1

����Ƕ��ʽϵ�y|�����~�R��1

�o

�P�I�~�� ���ٙ�Ŀ���OӋ����

������dȤ��

- ������

-

- �oԴ�����x�� 2024-10-10

- ACM6755 ֧��3�������õ�ȫ��������ֱ���oˢ늙C��IC���� 2024-10-09

- YXC�����Q�����������I���C���� 2024-09-27

- ��Դ����͟oԴ����ą^�e 2024-09-24

- ��ģ�K��Ȳ��p����ѕr�lCP-��־��� 2024-09-20

- ���w�C�����Ĺ���ԭ�� 2024-09-19

- YXCʯӢ��Դ��ֿɾ��̾����l�c200MHZ��С���c�ɾ��_����6λ��������5G��վ 2024-09-12

- 70V�͉����{OVP�ֵ���^�����oо-ƽоPW1600 2024-09-05

- YXC�P�d��Դ��Ʒ�l��ح1.2V�����ĕr犽�Q���� 2024-09-05

- YXC�P�d | 32.768KHZ�����x�ͷ��� 2024-09-02

- ���T�˺�

-

���ż����· ������·�D LED ���l�Ŵ����·�D ��Ƭ�C 늙C���� LED�·�D �����Դ �_�P�����Դ ����·�D ׃�l�� ��׃�� LED�����· ���{�S���g LED���·�D AV�Ŵ����· �ص����·�D 555���r�� 늴Št�·�D ���������· 51��Ƭ�C �·�OӋ �^�����o�· �^�����o�· �����· �ھ�Ӌ�� ���˷����· ��·���o�· �ŷ�늙C ���M늙C PIC��Ƭ�C ֱ�������Դ ���{�����Դ EMC ©늱��o�· Ƕ��ʽϵ�y ��Ȧ ���l��׃�� ���� ���{ UPS DC-DC�· �ضȂ����� 늴ż��� ���� ���l�_�P�Դ ���� EMI ��˹�� ���⾀